Bài giảng Thiết kế mạch số dùng HDL - Chương 4: Thiết kế luận lý với Verilog

lượt xem 4

download

Download

Vui lòng tải xuống để xem tài liệu đầy đủ

Download

Vui lòng tải xuống để xem tài liệu đầy đủ

Bài giảng Thiết kế mạch số dùng HDL - Chương 4: Thiết kế luận lý với Verilog có nội dung trình bày giới thiệu về HDLs và verilog; mô hình cấu trúc cho mạch luận lý tổ hợp; Mô phỏng luận lý, kiểm chứng thiết kế và phương pháp luận kiểm tra; thời gian trễ truyền lan;... Mời các bạn cùng tham khảo!

Bình luận(0) Đăng nhập để gửi bình luận!

Nội dung Text: Bài giảng Thiết kế mạch số dùng HDL - Chương 4: Thiết kế luận lý với Verilog

- dce 2008 Thiết kế mạch số với HDL Chương 4: Thiết kế luận lý với g Verilog

- 008 ng 20 Nội dung chính • Giới thiệu về HDLs và verilog • Mô hình cấu trúc cho mạch luận lý tổ hợp Engineerin • Mô phỏng luận lý, kiểm chứng thiết kế và ph ơng pháp lluận phương ận kiểm tra • Thời gian trễ truyền lan omputer E • Mô hình bảng sự thật cho mạch luận lý tổ hợp và tuần tự với Verilog Co Advanced Digital Design with the Verilog HDL – 2 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Nội dung chính • Giới thiệu về HDLs và verilog • Mô hình cấu trúc cho mạch luận lý tổ hợp Engineerin • Mô phỏng luận lý, kiểm chứng thiết kế và ph ơng pháp lluận phương ận kiểm tra • Thời gian trễ truyền lan omputer E • Mô hình bảng sự thật cho mạch luận lý tổ hợp và tuần tự với Verilog Co Advanced Digital Design with the Verilog HDL – 3 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Giới thiệu HDLs • HDLs (Hardware Description Languages) Không là một ngôn ngữ lập trình Engineerin Tựa C Thêm những chức năng mô hình hóahóa, mô phỏng chức năng Verilog vs vs. VHDL omputer E • Các bước thiết kế bằng HDL Mô tả mạch từ khóa Biên dịch để kiểm tra cú pháp (syntax) Mô phỏng hỏ để kiểm kiể tra t chức hứ năng ă củaủ mạch h Co Advanced Digital Design with the Verilog HDL – 4 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Engineerin Phương pháp luận thiết kế HDL Đặc tả bằng HDL Cấu trúc/hành vi của mạch Mô phỏng Tổng hợp omputer E Kiểm tra: thiết kế đã đúng yêu cầu chưa? Ánh xạ đặc tả thành các hiện thực Chức năng: Hành vi I/O Mức thanh ghil (Kiến trúcl) Mức luận lý (Cổng) Mức transistor (Điển tử) Timing: Waveform Behavior Co Advanced Digital Design with the Verilog HDL – 5 chapter 4 ©2008, Pham Quoc Cuong

- 008 Mô hình cấu trúc và mô hình hành vi trong HDLs ng 20 • Cấu trúc (Structural) chỉ tra cấu trúc phần cứng thật sự của mạch Engineerin Mức trừu tượng thấp ấ • Các cổng cơ bản (ví dụ and, or, not) • Cấu trúc phân cấp thông qua các module Tương tự lập trình hợp ngữ • Hành vi (Behavioral) chỉ ra hoạt động của mạch t ê các trên á bit bits omputer E Mức trừu tượng cao hơn • Biểu diễn bằng g các biểu thức ((ví dụ ụ out = ((a & b)) | c)) • Không phải tất cả các đặc tả hành vi đều tổng hợp được Không sử dụng: + - * / % > >= < >

- 008 ng 20 Những nguy hiểm trong thiết kế Verilog • Chương trình tuần tự, bộ tổng hợp có thể sẽ phải thêm nhiều chi tiết phần cứng Engineerin Cần ầ một bộ priority encoder • Nếu chương trình song song, có thể có những trạng thái không xác định Nhiều khối “always”, khối nào thực thi trước? • Tạo ạ ra nhiều trạng ạ g thái không g dự ự dịnh ị trước omputer E if (x == 1) out = 0; if (y == 1) out = 1; // else out retains previous state? R S latch! R-S • Không tính trước được số phần tử phần cứng x = x + 1 có thể cần RẤT NHIỀU phần tử phần cứng Co Advanced Digital Design with the Verilog HDL – 7 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Lịch sử phát triển HDLs • ISP (circa 1977) – dự án nghiên cứu CMU (Carnegie Mellon University) Mô phỏng nhưng không tổng hợp • Abel (circa 1983) – được phát triển bởi Data-I/O Engineerin Mục tiêu dùng cho các thiết bị luận lý khả lập trình Không tốt cho máy trạng thái • Verilog (circa 1985) – phát triển bởi Gateway (now Cadence) Đặc tả được đưa ra từ 1985 Ban đầu được phát triển cho mô phỏng phỏng, tương tự C và Pascal Hiệu quả và dễ viết Berkeley phát triển công cụ tổng hợp vào thập niên 80 Được IEEE chuẩn hóa • Verilog standardized (Verilog (Verilog-1995 1995 standard) omputer E • Verilog-2001 standard • VHDL (circa 1987) - DoD sponsored standard Dưa trên VHSIC phát triển bởi DARPA Tương tự như Ada (Nhấn mạnh vào tái sử dụng và bảo trì) Ngữ nghĩa mô phỏng rõ ràng Rất tổng quát nhưng dài dòng Được IEEE chuẩn hóa • VHDL standardized (’87 ( 87 and ’93) 93) Co Cấu trúc nghiêm ngặt Advanced Digital Design with the Verilog HDL – 8 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Verilog HDL • Verilog là một ngôn ngữ lớn Có nhiều tính năng cho tổng hợp và mô phỏng phần cứng Có thể biểu diễn những đặc trưng mức thấp Engineerin • Transistor Có thể hoạt động như ngôn ngữ lập trình • Cấu trúc lặp • Cấu trúc điều khiển…. • Các công cụ mô phỏng chấp nhận toàn bộ khái niệm của Verilog omputer E • Các công cụ tổng hợp chỉ chấp nhận một phần các khái niệm của Verilog • Chỉ tập trung nghiên cứu một phần ầ Sử dụng ở một mức thích hợp Tập trung trên những cấu trúc tổng hợp được Co Tập trung tránh những cấu trúc gây lỗi khi tổng hợp Advanced Digital Design with the Verilog HDL – 9 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Nội dung chính • Giới thiệu về HDLs và verilog • Mô hình cấu trúc cho mạch luận lý tổ Engineerin hợp • Mô phỏng lluận ận lý lý, kiểm chứng thiết kế và à phương pháp luận kiểm tra • Thời gian trễ ễ truyền ề lan omputer E • Mô hình bảng sự thật cho mạch luận lý tổ hợp và tuần tự với Verilog Co Advanced Digital Design with the Verilog HDL – 10 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Mô hình mạch tổ hợp • Một mô hình Verilog của một mạch tóm tắt các mô tả chức năng bằng góc nhìn cấu trúc hay Engineerin hà h vii ttrên hành ê những hữ mốiối quan hệ ngõõ vào-ngõ à õ ra • Một mô hình cấu trúc là một cấu trúc kết nối (netlist) chứa Các cổng Các khối chức năng omputer E • Một mô hình hành vi là Các biểu thức Boolean đơn giản Mô hì hìnhh chuyển h ể đổi mức ứ thanh h h ghihi (R (Register i T Transfer f Level – RTL) Một ộ ggiải thuật ậ Co Advanced Digital Design with the Verilog HDL – 11 chapter 4 ©2008, Pham Quoc Cuong

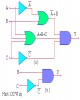

- 008 ng 20 Mô hình cấu trúc mạch tổ hợp • Thiết kế cấu trúc tương tự như tạo ra một sơ đồ Engineerin ( h (schematic) ti ) • Schematic Hình biểu diễn cổng logic, Ngõ vào ra, Các đường kết nối giữa các cổng cổng. omputer E • Mô hình cấu trúc HDL Danh sách các cổng cơ bản ả và kết ế nốiố giữa chúng Các phát biểu chỉ ra ngõ vào-ra Co Advanced Digital Design with the Verilog HDL – 12 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Verilog primitives • Primitives là các đối tượng cơ bản có thể được sử dụng trong thiết kế • 26 đối tượng chức năng được định nghĩa trước Engineerin n-output n-input p 3 t t 3-states and buf output kết thúc phát biểu nand not omputer E or bufif0 nand (y, a, b, c); nor bufif1 input keyword name xor notif0 xnor notif1 nand N1(y, (y, a,, b,, c); ); Ngõ ra là phần tử đầ đầu tiên trong Co danh sách các ngõ vào-ra instance name (optional) Advanced Digital Design with the Verilog HDL – 13 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Mô hình cấu trúc trong Verilog • Module Tên module và đi theo module module_name (port_list); sau là danh sách các //Declarations: Engineerin ngõ vào-ra (port) reg, wire, parameter, Danh sách đặc tả loại input, output, inout, port (input/output) function task, function, task … Danh sách các dây nối, //Statements: các biến sử dụng bên Initial statement trong module (optional) Always statement omputer E Danh sách các kết nối Module instantiation giữa các cổng và các Gate instantiation module khác bên trong g UDP instantiation endmodule Continuous assignment endmodule Co Advanced Digital Design with the Verilog HDL – 14 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Ví dụ Module ports Engineerin port modes Internal wires Instantiated primitives omputer E Co Advanced Digital Design with the Verilog HDL – 15 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Module ports • Giao tiếp với “môi trường” bên ngoài • Kiểu của port quyết định chiều truyền dữ Engineerin liệu Một ộ chiều (Unidirectional) ( ) • input • output Hai chiều ề (Bidirectional) ( ) omputer E • inout • Kiểu của module port phải được khai báo tường minh và không cần theo thứ tự xuất hiện trong port list Co Advanced Digital Design with the Verilog HDL – 16 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Quy tắt trong Verilog • Phân biệt chữ hoa thường (Case sensitive) de e a • Identifier: a-z,, A-Z,, 0-9, 0 9, ‘_’ và à ‘$’ $ Engineerin • Tên biến không được bắt đầu bằng ‘$’ hay ký số và có thể tối đa là 1024 kýý tự ự • Một phát biểu được kết thúc bằng ‘;’ • Chú thích omputer E ‘//’ một dòng chú thích /*…*/ chú thích nhiều dòng • Các identifiers có phạm vi nhất định • Có thể viết các pphát biểu trên một ộ dòng g hay y Co nhiều dòng Advanced Digital Design with the Verilog HDL – 17 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Thiết kế từ trên xuống (top-down) • Hệ thống phức tạp được phân chia thành những đơn vị chức năng nhỏ hơn Dễ thiết kế Engineerin Dễ kiểm tra • Các module lồng nhau trong Verilog hỗ trợ thiết kế ế từ trên xuống ố • Module tham khảo đến module khác được gọi là module “cha” cha , module được module khác tham omputer E khảo đến gọi là module “con” • Độ sâu của các module lồng nhau không giới hạn • Mỗi module con phải có tên duy nhất trong phạm p ạ vi module cha (trừ ( các primitives) p ) Co Advanced Digital Design with the Verilog HDL – 18 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Binary full adder M2 a b c_in c_in a sum sum Half adder Half_adder Engineerin a a sum w1 w3 b c_out Half_adder c_out w2 b b c_out M1 omputer E Co Advanced Digital Design with the Verilog HDL – 19 chapter 4 ©2008, Pham Quoc Cuong

- 008 ng 20 Thiết kế phân cấp và tổ chức mã nguồn • Top-level module là module ở cấp cao nhất Engineerin • Module ở mức thấp nhất Chứa các primitives Các module không phân chia nhỏ hơn • Tất cả ả các á module d l đđược đặt trong t một ột hay h omputer E nhiều tập tin khác nhau • Công cụ mô phỏng tích hợp các module từ các tập tin Co Advanced Digital Design with the Verilog HDL – 20 chapter 4 ©2008, Pham Quoc Cuong

CÓ THỂ BẠN MUỐN DOWNLOAD

-

Bài giảng Thiết kế logic số (VLSI design): Chương 1 - Trịnh Quang Kiên

29 p |

29 p |  206

|

206

|  24

24

-

Bài giảng Thiết kế mạch Logic và Analog

82 p |

82 p |  149

|

149

|  15

15

-

Bài giảng Thiết kế logic số (VLSI design): Chương 2.5 - Trịnh Quang Kiên

18 p |

18 p |  153

|

153

|  14

14

-

Bài giảng Thiết kế logic số (VLSI design): Chương 4.1 - Trịnh Quang Kiên

29 p |

29 p |  176

|

176

|  9

9

-

Bài giảng Thiết kế logic số (VLSI design): Chương 4.2 - Trịnh Quang Kiên

23 p |

23 p |  119

|

119

|  9

9

-

Bài giảng Thiết kế mạch điện tử: Phần 2 - Trường Đại học Thái Bình

81 p |

81 p |  15

|

15

|  8

8

-

Bài giảng Thiết kế mạch điện tử: Phần 1 - Trường Đại học Thái Bình

37 p |

37 p |  20

|

20

|  6

6

-

Bài giảng Thiết kế mạch logic: Chương 1 và 2

28 p |

28 p |  127

|

127

|  5

5

-

Bài giảng Thiết kế logic số: Lecture 4.1 - TS. Hoàng Văn Phúc

19 p |

19 p |  83

|

83

|  4

4

-

Bài giảng Thiết kế mạch số dùng HDL - Chương 6: Tổng hợp mạch luận lý tổ hợp và tuần tự

91 p |

91 p |  32

|

32

|  4

4

-

Bài giảng Thiết kế logic số: Lecture 4.5 - TS. Hoàng Văn Phúc

22 p |

22 p |  89

|

89

|  3

3

-

Bài giảng Thiết kế logic số: Lecture 4.2 - TS. Hoàng Văn Phúc

22 p |

22 p |  76

|

76

|  3

3

-

Bài giảng Thiết kế mạch số dùng HDL - Chương 2: Thiết kế mạch luận lý tổ hợp

45 p |

45 p |  23

|

23

|  2

2

-

Bài giảng Thiết kế mạch số dùng HDL - Chương 1: Phương pháp luận thiết kế vi mạch số

24 p |

24 p |  38

|

38

|  2

2

-

Bài giảng Thiết kế mạch số dùng HDL - Chương 7: Thiết kế và tổng hợp bộ điều khiển dòng dữ liệu

28 p |

28 p |  44

|

44

|  2

2

-

Bài giảng Thiết kế mạch số dùng HDL - Chương 9: Giải thuật và kiến trúc cho các bộ xử lý số

46 p |

46 p |  35

|

35

|  2

2

-

Bài giảng Thiết kế mạch số dùng HDL - Chương 3: Thiết kế mạch luận lý tuần tự

41 p |

41 p |  30

|

30

|  2

2

Chịu trách nhiệm nội dung:

Nguyễn Công Hà - Giám đốc Công ty TNHH TÀI LIỆU TRỰC TUYẾN VI NA

LIÊN HỆ

Địa chỉ: P402, 54A Nơ Trang Long, Phường 14, Q.Bình Thạnh, TP.HCM

Hotline: 093 303 0098

Email: support@tailieu.vn